An Efficient FPGA Architecture for Reconfigurable FFT Processor Incorporating an Integration of an Improved CORDIC and Radix-2r Algorithm | SpringerLink

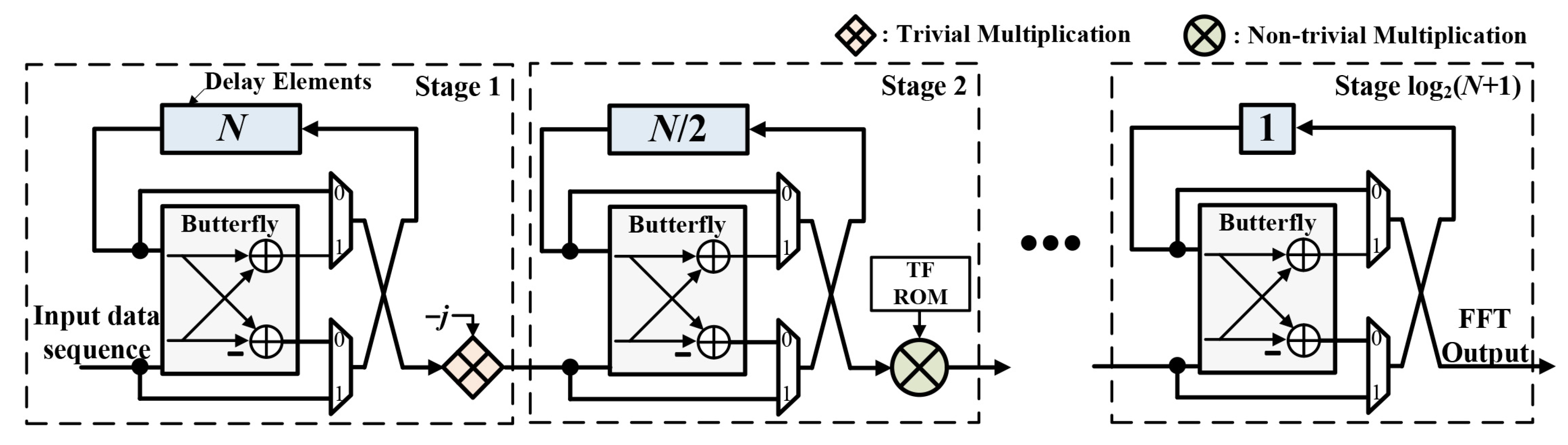

Electronics | Free Full-Text | A Pipelined FFT Processor Using an Optimal Hybrid Rotation Scheme for Complex Multiplication: Design, FPGA Implementation and Analysis

Low‐power fast Fourier transform hardware architecture combining a split‐radix butterfly and efficient adder compressors - Ferreira - 2021 - IET Computers & Digital Techniques - Wiley Online Library

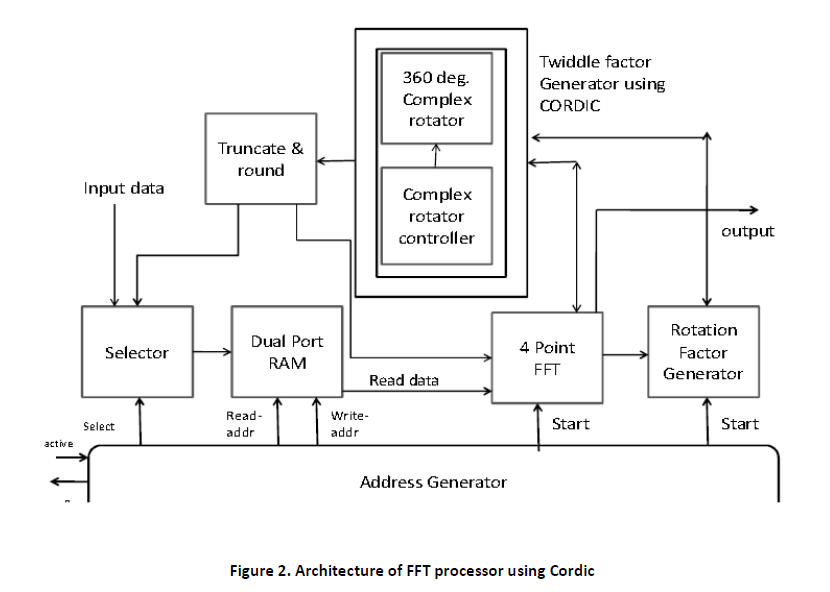

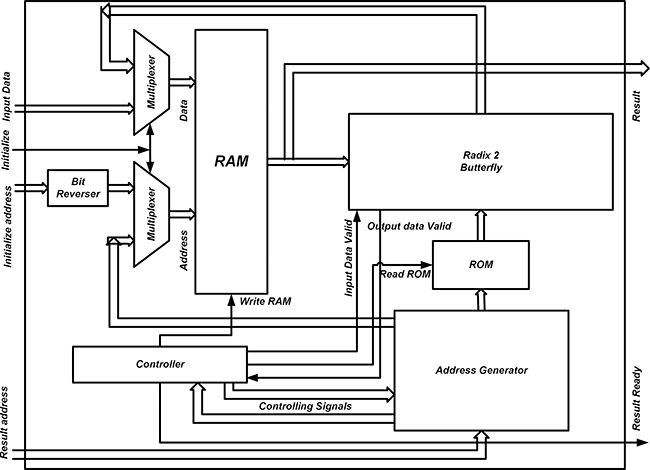

![PDF] Hardware Implementation of Decimation in Time FFT | Semantic Scholar PDF] Hardware Implementation of Decimation in Time FFT | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/9084a51d644e1ab1cdad82d2075f05b6d88b468e/2-Figure2-1.png)