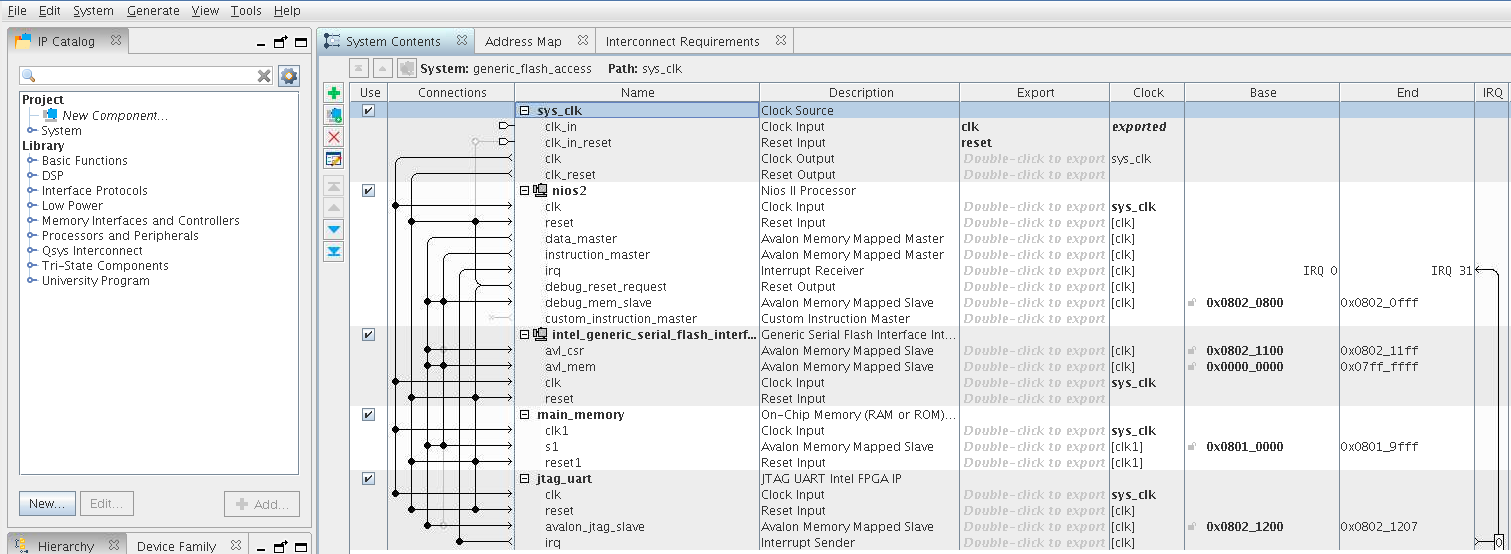

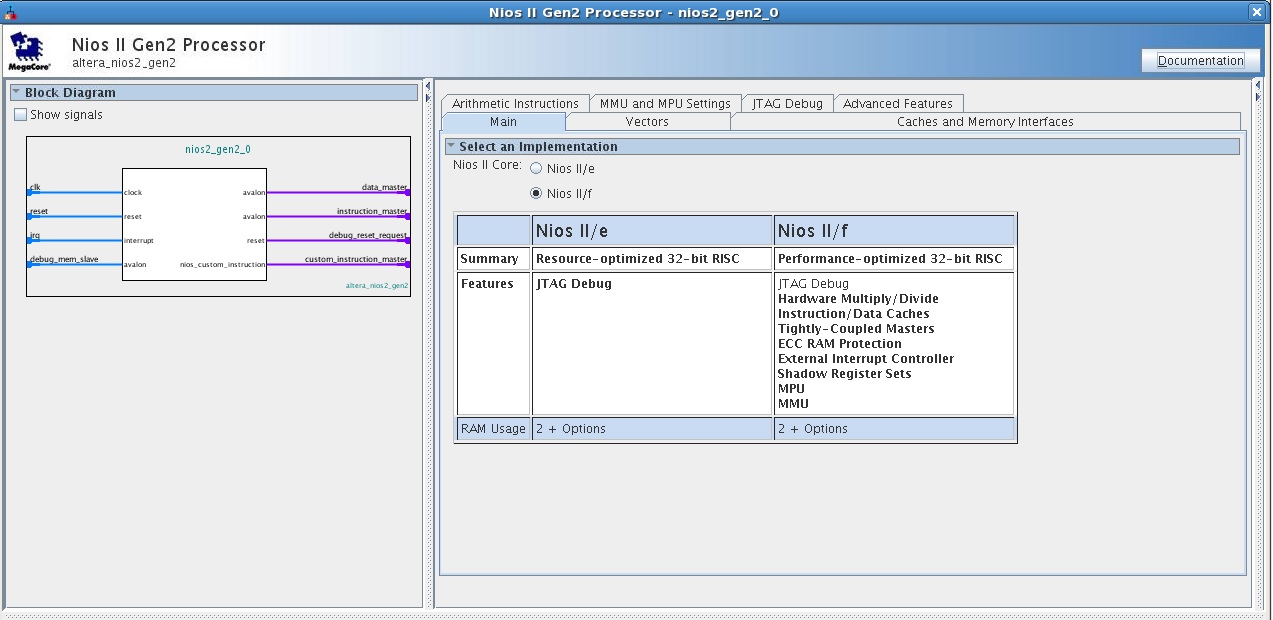

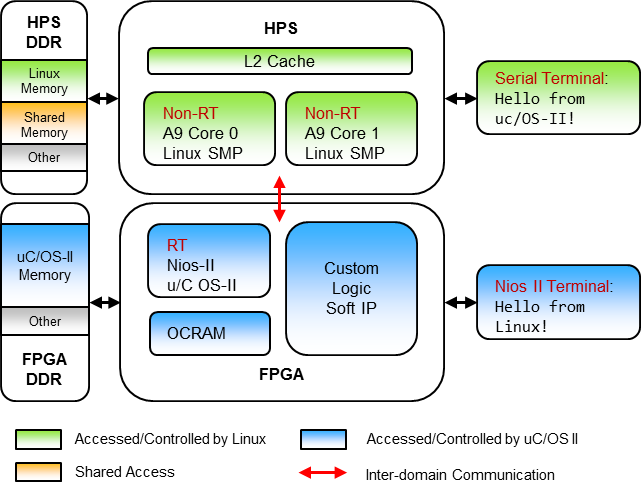

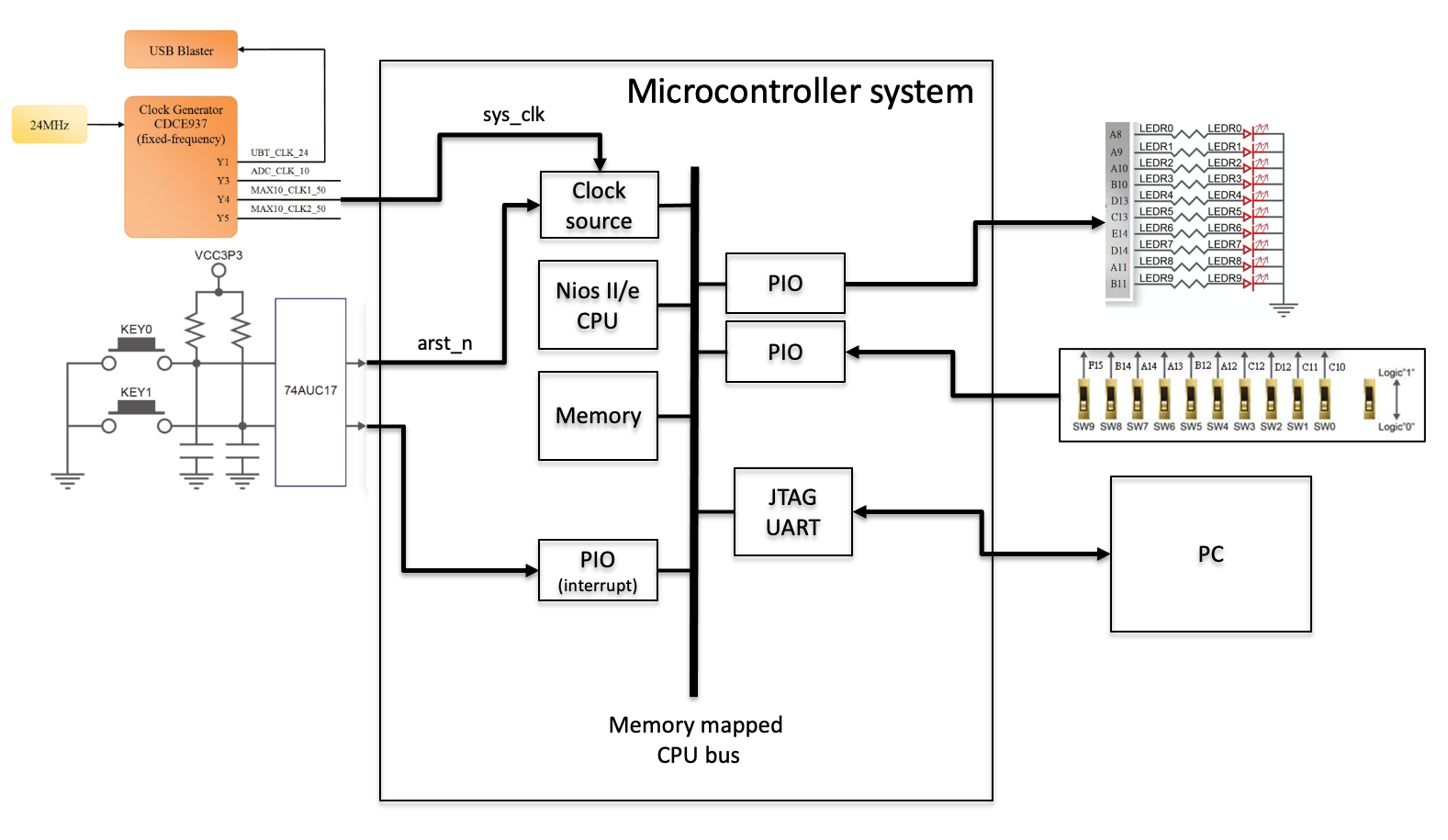

Electronics | Free Full-Text | XML-Based Automatic NIOS II Multi-Processor System Generation for Intel FPGAs

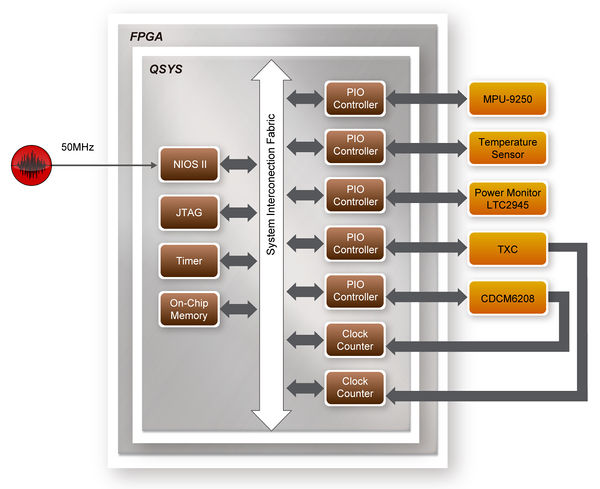

DE10 Advance revC demo: Nios II control for Programmable PLL/Temperature/Power/9-axis - Terasic Wiki

Simulating ALTERA NIOS II Embedded Processor Designs in Active-HDL - Application Notes - Documentation - Resources - Support - Aldec

Soft Core Processor Using Fpga: Nios II Soft Core Processor Using High Designed Tools: Pokale, Sangita: 9783659408175: Amazon.com: Books

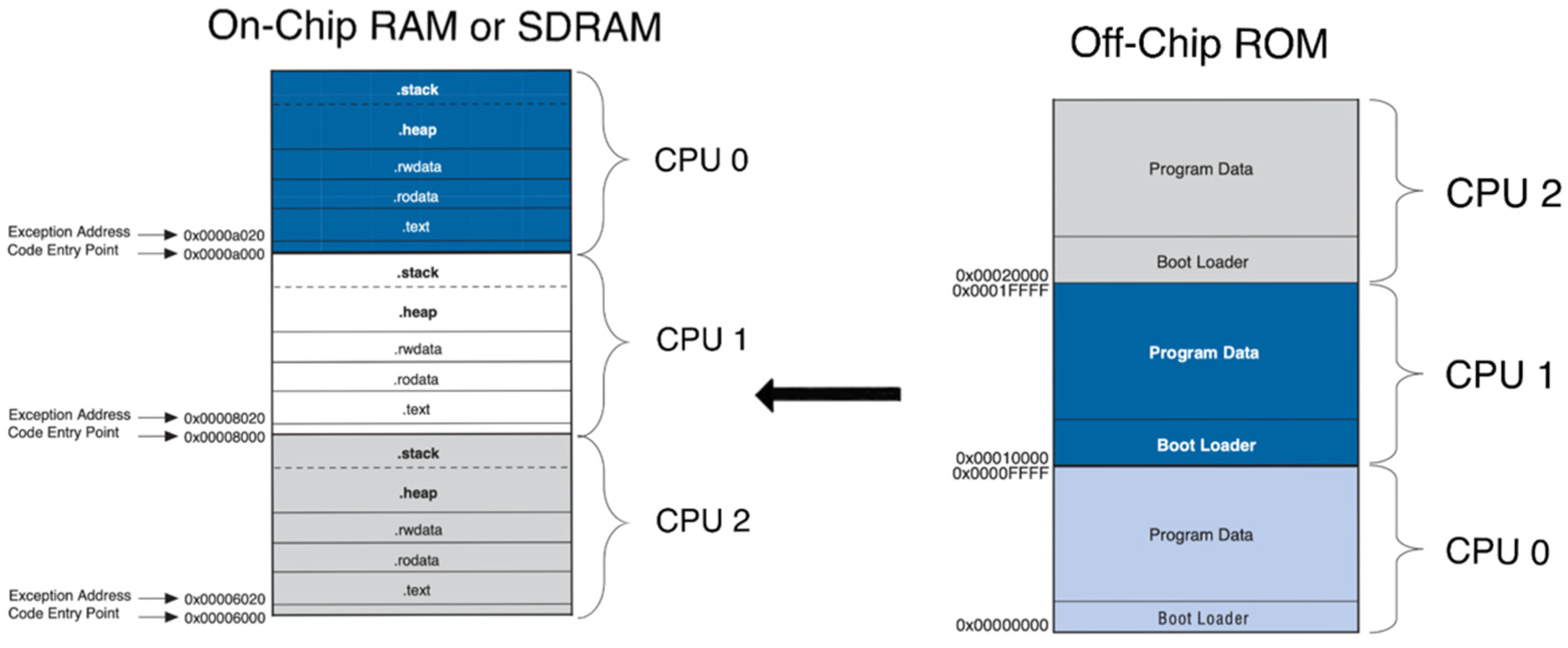

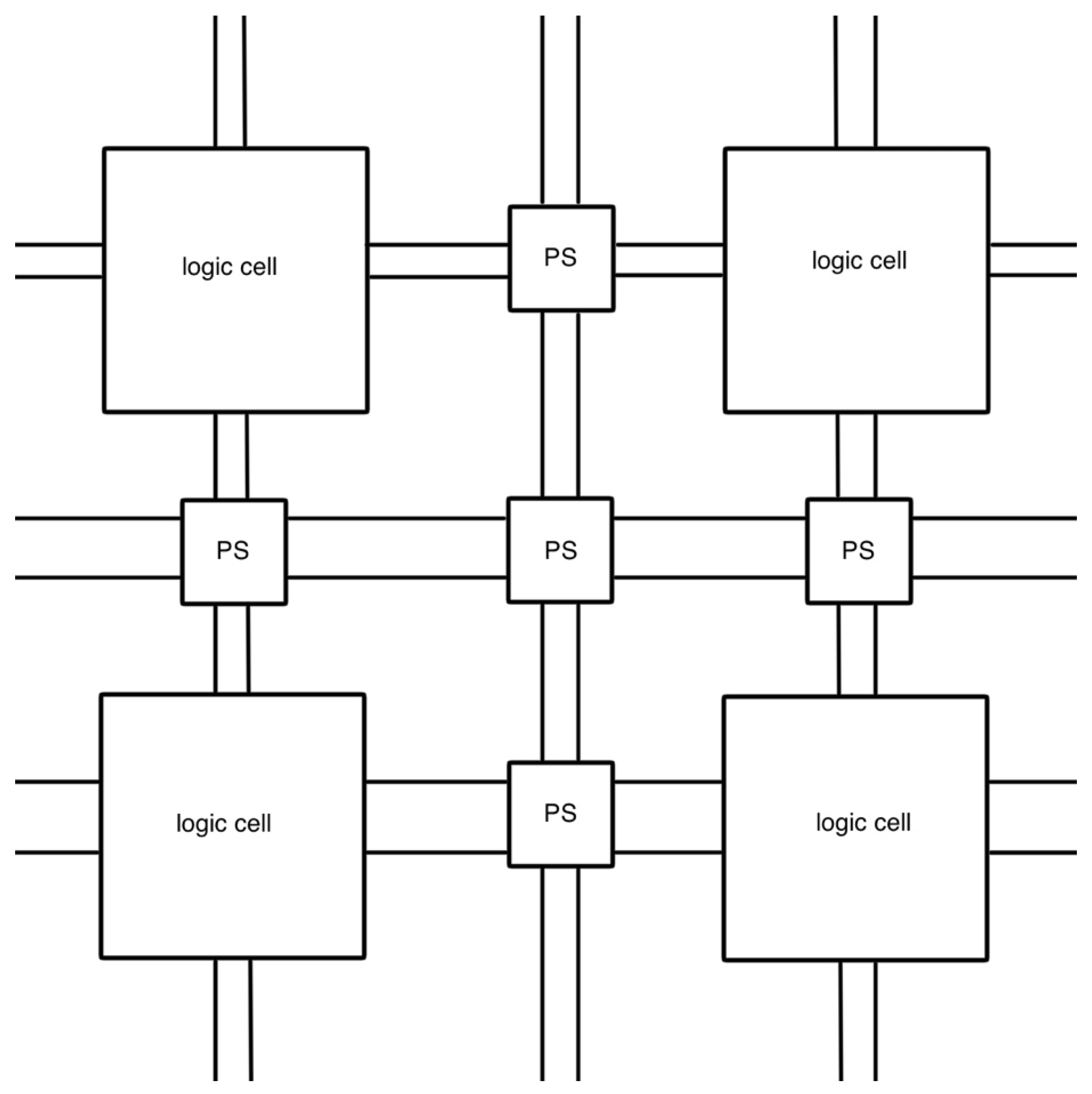

Electronics | Free Full-Text | XML-Based Automatic NIOS II Multi-Processor System Generation for Intel FPGAs

GitHub - ptresearch/nios2: IDA Pro processor module for Altera Nios II Classic/Gen2 microprocessor architecture